# FAST AND EFFICIENT LOSSLESS IMAGE COMPRESSION BASED ON CUDA PARALLEL WAVELET TREE ENCODING

by

Jingqi Ao, B.S.E.E, M.S.E.E

A Dissertation

In

## ELECTRICAL AND COMPUTER ENGINEERING

Submitted to the Graduate Faculty of Texas Tech University in Partial Fulfillment of the Requirements for the Degree of

## DOCTOR OF PHILOSOPHY

Approved

Dr. Sunanda Mitra Committee Chair

Dr. Brian Nutter, Co-chair

Dr. Ranadip Pal

Dr. Mark A. Sheridan Dean of the Graduate School

May, 2014

## ACKNOWLEDGMENTS

First, my gratitude is due to my advisor Dr. Sunanda Mitra. Dr. Mitra is always there when I need help and she is more like a mentor rather than a professor to me. One of most valuable things I learned from her is her spirit, never stop learning new things and never quit. I would also like to thank Dr. Brian Nutter and Dr. Ranadip Pal. They are like my elder friends. Besides knowledge, they selflessly share their experiences and ideas with me. I also really appreciate their valuable time spent as my committee members.

Then, I would like to thank my friends at CVIAL: Dr. Enrique Corona, Bharath Lohray and Xiangyuan Zhao. From you, I learnt about different cultures, different countries, and different opinions. You let me know how huge the world is and how broad our field is.

Last but not the least, I would like to thank my parents. I miss you so much. Thank you for your support and understanding during my six-year study. We all made sacrifices but I always know that without you, there is no chance for this dissertation.

## TABLE OF CONTENTS

| ACKNOWLEDGMENTSii                                             |

|---------------------------------------------------------------|

| Abstractv                                                     |

| LIST OF TABLESvi                                              |

| LIST OF FIGURESvii                                            |

| CHAPTER I. INTRODUCTION                                       |

| CHAPTER II. BACKGROUND OF BCWT AND GPGPU MODELS5              |

| 2.1 The Sequential BCWT                                       |

| 2.2 General Purpose Graphic Processing Unit (GPGPU) Computing |

| 2.2.1 CUDA Memories8                                          |

| 2.2.2 Threads and Thread Divergence10                         |

| 2.2.3 Synchronization12                                       |

| CHAPTER III. PCWT COMPRESSION PROCEDURE 14                    |

| 3.1 Parallel B-LDWT+B                                         |

| 3.1.1 (5,3)-LDWT                                              |

| 3.1.2 Parallel B-LDWT+B16                                     |

| 3.1.3 Implementation of Horizontal 2D B-LDWT+B21              |

| 3.1.4 Implementation of Vertical 2D B-LDWT+B23                |

| 3.2 Parallel MQD calculation                                  |

| 3.2.1 Modified MQD calculation                                |

| 3.2.2 Implementation of Parallel MQD Calculation30            |

| 3.3 Parallel Qmax search                                      |

| 3.3.1 Qmax and parallel maximum value search33                |

| 3.3.2 Implementation of horizontal reduction                  |

| 3.3.3 Implementation of vertical reduction                    |

| 3.3.4 Implementation of final reduction                       |

| 3.4 Parallel Element Encoding                                 |

| 3.4.1 Elements in Parallel Element Encoding41                 |

| 3.4.2 Element Encoding Sequence and Rules42                   |

| 3.4.3 Implementation of Parallel Element Encoding             |

| 3.5 Parallel Group Encoding                                   |

| 3.5.1 Group Encoding 54                                       |

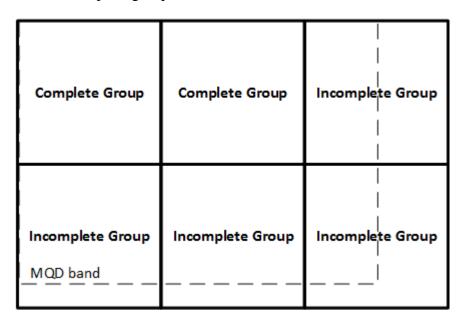

| 3.5.2 Complete and incomplete group                               | 57  |

|-------------------------------------------------------------------|-----|

| 3.5.3 Complete and incomplete blocks                              | 59  |

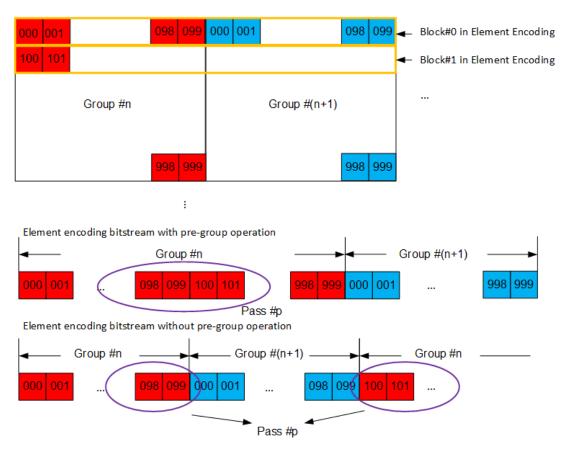

| 3.5.4 Pre-group operation in Element Encoding Stage               | 59  |

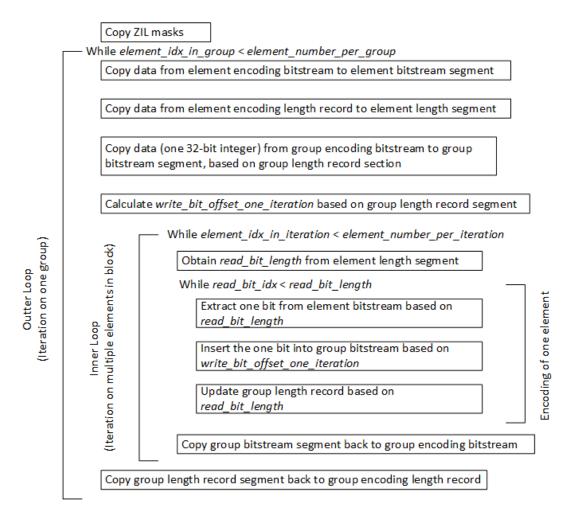

| 3.5.5 Implementation of Parallel Group Encoding                   | 60  |

| 3.5 Sequential Bitstream Output                                   | 63  |

| 3.5.1 Sequential Output                                           | 63  |

| 3.5.2 Implementation of Sequential Output                         | 64  |

| CHAPTER IV. PCWT DECOMPRESSION PROCEDURE                          | 65  |

| 4.1 Sequential Bitstream Input                                    | 65  |

| 4.1.1 Sequential Input                                            | 65  |

| 4.1.2 Implementation of Sequential Bitstream Input                | 65  |

| 4.2 Sequential Decoding                                           | 66  |

| 4.2.1 Sequential decoding and its comparison with encoding stages | 66  |

| 4.2.2 Implementation of sequential decoding                       | 69  |

| 4.3 Parallel Inverse B-LDWT+B                                     | 71  |

| 4.3.1 Implementation of Vertical 2D B-LDWT+B                      | 73  |

| 4.3.2 Implementation of Horizontal Inverse 2D B-LDWT+B            | 74  |

| 4.4 Codec Properties Calculation                                  | 74  |

| 4.4.1 Codec Properies                                             | 74  |

| 4.4.2 Codec Properties Calculation in Compression Procedure       | 76  |

| 4.4.3 Codec Properties Calculation in Decompression Procedure     | 83  |

| CHAPTER V. COMPARATIVE EXPERIMENTAL RESULTS OF PCWT               |     |

| AND JPEG-XR                                                       |     |

| CHAPTER VI CONCLUSIONS AND FUTURE WORK                            |     |

| Dini 1000 Aniiy                                                   | 0.4 |

## **ABSTRACT**

Lossless compression is still in high demand in medical image applications despite improvements in the computing capability and decrease in storage cost in recent years. With the development of General Purpose Graphic Processing Unit (GPGPU) computing techniques, sequential lossless image compression algorithms can be modified to achieve more efficiency and speed. Backward Coding of Wavelet Trees (BCWT) is an efficient and fast algorithm, utilizing Maximum Quantization of Descendants (MOD) and it is quite suitable for lossless parallel compression because of its intrinsic parallelism and simplicity. However, the original implementation of BCWT is a CPU-based sequential codec and that implementation has multiple drawbacks which hinder the parallel extension of BCWT. Parallel Coding of Wavelet Trees (PCWT) modifies the BCWT from theoretical workflow to implementation details. PCWT introduces multiple new parallel stages, including parallel wavelet transform stage, parallel MQD calculation stage, parallel Qmax search stage, parallel element encoding stage and parallel group encoding stage, and change the encoding sequence from backward to forward. All those stages are designed to accelerate the compression process. PCWT implementation is designed with the consideration of Compute Unified Device Architecture (CUDA) hardware constrains and implementation scalability. With newly designed workflow and highly optimized parallel stages, PCWT performs faster than the lossless JPEG-XR algorithm, the current standard, with comparable compression ratios. Multiple possible improvements in speed and flexibility on PCWT are also proposed as future work.

## LIST OF TABLES

| 5.1 Test image information                                                                                                      | 88 |

|---------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2 Compression ratio, compression running time and decompression running time of 20 test images by using PCWT and JPEG-XR      | 90 |

| 5.3 Weighted compression acceleration, weighted decompression acceleration and weighted size overhead for four image categories | 91 |

## LIST OF FIGURES

| 2.1. CUDA memory architecture                                                                                                           | 8    |

|-----------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.2 Comparison between coalescing and non-coalescing memory access of 256-byte data in the global memory                                | 9    |

| 3.1 Forward 1D B-LDWT+B transform on 12 elements with 3 blocks                                                                          | . 16 |

| 3.2 Band and level size calculation                                                                                                     | . 18 |

| 3.3 Example of horizontal 2D B-LDWT+B                                                                                                   | . 23 |

| 3.4 Comparison between column-wise and row-wise 2D matrix processing                                                                    | . 25 |

| 3.5 Example of vertical 2D B-LDWT+B                                                                                                     | . 27 |

| 3.6 Calculation of two types of MQD bands                                                                                               | . 29 |

| 3.7 Example of parallel MQD calculation                                                                                                 | . 32 |

| 3.8 Three main phases of parallel Qmax search                                                                                           | . 34 |

| 3.9 An example of horizontal reduction                                                                                                  | . 36 |

| 3.10 Example of vertical reduction                                                                                                      | . 39 |

| 3.11 Example of final reduction                                                                                                         | . 41 |

| 3.12 The encoding sequence of element encoding                                                                                          | . 43 |

| 3.13 Example of element encoding with Qmax                                                                                              | . 44 |

| 3.14 Example of element encoding with higher-level MQD                                                                                  | . 46 |

| 3.15 ZIR and ZIL groups and opposite index directions in MQD, coefficients and bitstream                                                | . 47 |

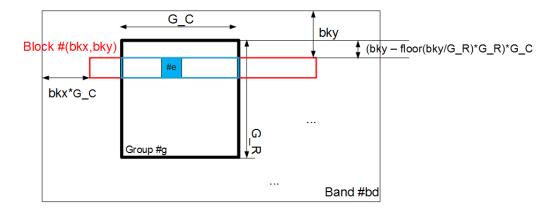

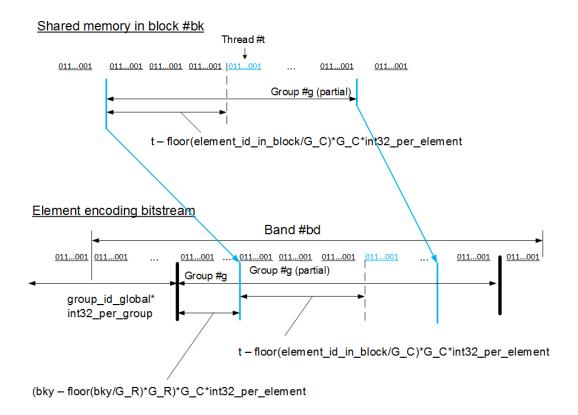

| 3.16 One element in band #bd, group #g is processed by thread t in block #(bkx, bky)                                                    | . 50 |

| 3.17 Relationship between one 32-bit integer in shared memory of block #bk and one 32-bit integer in the element encoding bitstream     | . 52 |

| 3.18 Relationship between one 32-bit integer in shared memory of block #bk and one 32-bit integer in the element encoding length record | . 53 |

| 3.19 Example of processing one block in element encoding stage                                                                          | . 54 |

| 3.20 Example of correct group encoding bitstream and incorrect group encoding bitstream caused by race condition                        | . 55 |

| 3.21 Complete and incomplete groups for MQD band                                                                                        | . 57 |

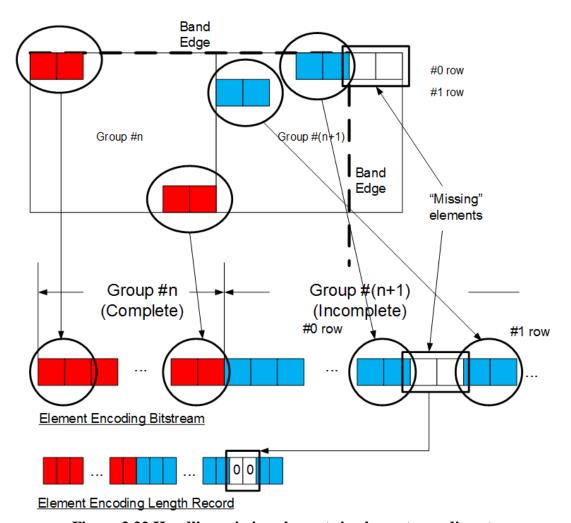

| 3.22 Handling missing elements in element encoding stage                                                                                | . 58 |

| 3.23 Comparison between element encoding bitstream with and without pre-group operation | 60 |

|-----------------------------------------------------------------------------------------|----|

| 3.23 Main steps in group encoding stage                                                 | 62 |

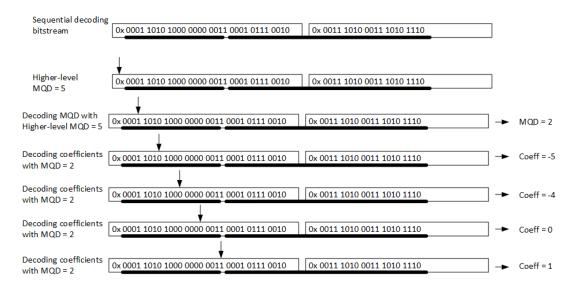

| 4.1 Example of decoding one element with the corresponding higher-level MQD.            | 68 |

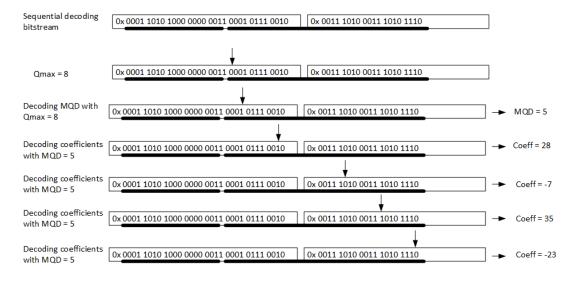

| 4.2 Example of decoding one element with QMAX                                           | 68 |

| 4.3 The implementation of sequential decoding                                           | 70 |

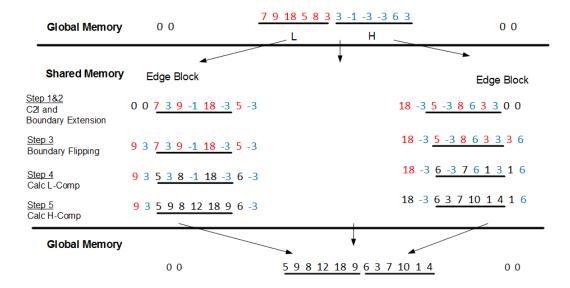

| 4.4 Example of 1D inverse B-LDWT+B                                                      | 73 |

| 4.5 Calculation of level size, level offset, band size and band offset                  | 77 |

| 4.6 Effect of coefficient band offset in B-LDWT+B                                       | 81 |

| 4.7 Bitstream related codec properties                                                  | 82 |

| 4.8 The codec properties calculation in decompression procedure                         | 84 |

| 5.1 The workflow diagram of JPEG-XR algorithm                                           | 85 |

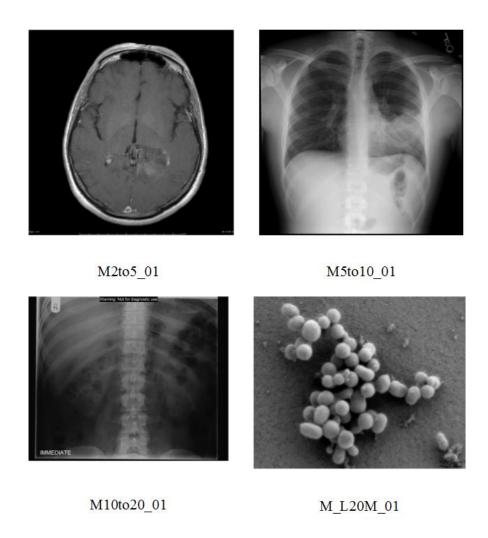

| 5.2 Four sample images used in the comparison                                           | 89 |

## **CHAPTER I**

### INTRODUCTION

The explosion of image data nowadays has demanded advanced image compression algorithms to be implemented in both image transmission and image storage stages. For example, for medical images, 600 million imaging procedures are performed in United States every year and they are taking more space than before since more complex imaging techniques have been applied [1]. Cloud storage has been proposed to address the efficiency problem of image storage and access and image compression algorithm is one of key techniques for cloud-based solution. Cloud-based solution requires scalability and consistency, which implies multiple copies of large image datasets [2]. Cloud-based solution also allows flexible data access, which means data should be able to be accessed conveniently with Wi-Fi and 3G/4G connections [2]. However, those accesses are relatively slow and expensive. In general, data transmission time during the access should be short, which requires the image data should be compressed and reusable.

One of most popular standards for image compression is Joint Picture Expert Group (JPEG) [3]. It has been widely used in digital cameras and on Internet. However, JPEG is intrinsically lossy because it is based on the lossy Discrete Cosine Transform (DCT) [3] and it is not suitable for many high-precision-required applications. The successor of JPEG is JPEG2000 [4], with the ambition of improving JPEG with another transform, i.e. Discrete Wavelet Transform (DWT) [4]. However, JPEG 2000 is overly complicated and is not widely applied in image processing field. The latest image compression standard is JPEG-XR [5], utilizing so called hierarchical two-stage Lapped Biorthogonal Transform (LBT) [6]. LBT is similar to DCT except it can be lossless. JPEG-XR is quite new and still needs time to be widely accommodated.

One distinguishing feature of DWT is the pyramid structure of its result [7]. DWT has the concept "level" and pyramid structure of its result reflects the

independency within one level and dependency between neighboring levels. Dependency between neighboring levels can be utilized in compression and more importantly, independency within one level can be utilized to achieve high degree of parallelism, which implies fast compression. In this dissertation, Parallel Coding of Wavelet Trees (PCWT) is proposed, as a DWT-based compression algorithm, to achieve high speed compression, with competitive compression efficiency to JPEG-XR standard.

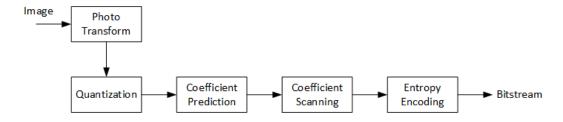

DWT-based compression generally includes two procedures: compression procedure and the corresponding decompression one. The compression procedure usually has two phases: forward transform phase and encoding phase. The transform phase is to generate wavelet coefficients via forward DWT and the encoding phase is to encode those coefficients into bitstream. The decompression procedure also includes two phases: decoding phase and inverse transform phase. The decoding phase is to restore wavelet coefficients from bitstream and the inverse transform phase is to restore original data by performing inverse DWT.

DWT-based compression can be either lossy or lossless, depending on whether restored data are mathematically equal to original data. "Mathematical equivalency emphasizes on the numerical identity between restored data and original data. There is a type of lossy compression, called visually lossless compression [8], in which restored data, i.e. restored images, are not the same as original data, i.e. original images, but differences between restored images and original images are difficult to be perceived by human visual system.

Lossless DWT-based compression is the basis of its lossy counterparts. Any change on any part of lossless compression can lead to a lossy compression.

Nonetheless, not all types of losses are acceptable. Note that PCWT is implemented as a lossless compression, which can provide a base-line compression for any further modification or improvement. However, it can also be easily implemented in a lossy compression mode.

For PCWT, in transform phase, the reversible (5,3) wavelet transform is used for lossless compression [9]. (5,3) wavelet transform is an integer to integer transform so that integer pixel values from images can be transformed to integer coefficients losslessly. Lifting scheme can be used in the implementation of (5,3) wavelet transform, which requires less memory and computation than the traditional convolution method [10].

In encoding phase, Backward Coding of Wavelet Trees (BCWT) [11] is chosen among other wavelet coefficient encoding algorithms such as SPIHT [12], or EBCOT [13]. BCWT is an efficient and fast algorithm, by utilizing Maximum Quantization Descendant (MQD) in its one-pass encoding procedure. However, the original BCWT implementation is a CPU-based sequential program. In PCWT, its main concepts have been maintained but several main steps have been modified to achieve high parallelism.

Recently, General Purpose Graphic Processing Unit (GPGPU) computing has been increasingly used to accelerate traditionally sequential procedures [14]. GPGPU computing has been proposed to be utilized in some image compression standards, such as JPEG2000 [15] and JPEGXR [16]. However, some aspects of those standards were not designed with the consideration of parallelism, e.g. entropy coding, which are difficult to be parallelized. On the other hand, BCWT can be a good candidate for lossless parallel wavelet transform based compression because of its intrinsic parallelism and simplicity [11]. That is also an important reason why BCWT is chosen as the encoding phase.

The main research contributions of this dissertation are 1) development of an accelerated compression algorithm i.e., PCWT within the context of GPGPU demonstrating a GPGPU approach to solve existing sequential problems, 2) modifications and re-designs made to eliminate or at least relieve the impacts of GPGPU disadvantages on our final algorithm, without largely sacrificing its advantages thus including Block-wise Lifting-scheme Discrete Wavelet Transform with Boundary processing (B-LDWT+B) and two-stage encoding and excluding line-

based implementation of BCWT [17] due to its nonadaptive, irregular result generation pattern and intensive I/O accesses, 3) backward coding for MQD computation only, otherwise, forward coding of wavelet trees, and 4) superior performance of PCWT over current standard, JPEG-XR, for large images (over 20 mega pixels) in encoding speed.

This dissertation is organized as follows: Chapter 1 briefly introduces the importance of image compression and reviews the development of image compression standard. It also provides an overview of the proposed PCWT and relevant techniques and outlines the main contributions of this dissertation work. Chapter 2 illustrates background knowledge about BCWT, i.e. the predecessor of PCWT, and the GPGPU computing model used in this dissertation. Chapter 3 and 4 describe the implementation details of PCWT in terms of compression procedure and decompression procedure, respectively. Chapter 5 demonstrates test results of PCWT, which is compared with those of a mainstream JPEG-XR implementation. Chapter 6 concludes the dissertation by providing the conclusion of dissertation and possible future work.

## **CHAPTER II**

## BACKGROUND OF BCWT AND GPGPU MODELS

## 2.1 The Sequential BCWT

The BCWT was originally implemented as a sequential CPU-based algorithm. One major improvement brought by BCWT is the simplified encoding algorithm, in which multiple wavelet tree searches are eliminated. The encoding is only based on MQD, which allows the local encoding. MQD is defined in [17] as:

$$m_{i,j} = \begin{cases} q_{O(i,j)}, & \text{if } (i,j) \text{ is in level 2 subbands }, \\ \max\{q_{O(i,j)}, \max_{(k,l) \in O(i,j)} (m_{k,l})\}, & \text{otherwise} \end{cases}$$

in which

c<sub>i,i</sub>: The wavelet coefficient at coordinate (i, j).

O(i, j): A set of coordinates of all the offspring of (i,j).

D(i, j): A set of coordinates of all descendants of (i,j).

L(i, j) = D(i, j) - O(i, j): A set of coordinates of all the leaves of (i, j).

$$q_{i,\,j} = \begin{cases} \left\lfloor \log_2 \left| c_{i,\,j} \right| \right\rfloor \text{ ,if } \left| c_{i,\,j} \right| \geq 1 \text{ : The quantization level of the coefficient } c_{i,\,j} \right. \\ \text{, otherwise} \end{cases}$$

$q_{O(i,j)} = \max_{(k,l) \in O(i,j)} \left\{ q_{k,l} \right\}$ : The maximum quantization level of the offspring of (i,j).

$q_{{\scriptscriptstyle L(i,j)}} = \max_{\scriptscriptstyle (k,l) \in {\scriptscriptstyle L(i,j)}} \{q_{\scriptscriptstyle k,l}\} \text{ : The maximum quantization level of the leaves of (i,j).}$

Local encoding has two meanings: one is within each coefficient band, to encode each MQD based unit, i.e. one MQD and its corresponding four coefficients, only the MQD based unit and one higher-level MQD are involved. Neither extra neighboring coefficient nor MQD is needed. The other meaning is to encode bands on

any level, only two levels, i.e. the current level and the adjacent higher level, are involved. There is no operation that involves more than two levels.

Local encoding introduces parallelism in BCWT because multiple local encoding operations can run simultaneously. However, even though the parallelism of BCWT was mentioned [11], there is no parallel implementation of BCWT, to the best of knowledge of the author.

One possible difficulty that hinders parallel implementation of BCWT is the parallel generation of bitstreams. Bitstream generation is usually the bottleneck of most image processing algorithms, because no matter how many parts of an image can be processed in parallel, the final bitstream is always sequential and can only be generated sequentially. Another possible difficulty is the cost of penalization. In this dissertation, GPGPU computing model is chosen as the parallel computing model. However, there are multiple new implementation issues for GPGPU computing model to implement BCWT, which do not exist or have little effects in CPU-based sequential implementation. For example, one of most significant issues is the decomposition level of forward wavelet transform used in BCWT. In CPU-based sequential implementation, the number of decomposition levels can be very high, which generates small size of bands on the top level. But in GPGPU computing model, those small bands can jeopardize the overall performance of algorithm. Another example is the use of MQD in BCWT. In one BCWT CPU-based sequential implementation [17], MQD is used to encode coefficients for all bands except top-level bands, i.e. LL, HL, LH and HH bands on the top level. Those bands have their own encoding rules. However, in this dissertation's implementation, pre-allocation of GPU memory prefers estimable and unified MQD-based coefficient encoding rules, by which all coefficients are encoded in the same way so that the overall required size of generated bitstream is easy to be estimated.

In BCWT CPU-based sequential implementation, the encoding sequence is backward, which is from the lowest level to the highest level of coefficient matrix. The backwardness of BCWT aims to decrease resource usage of the algorithm, more specifically, low memory usage during the compression procedure. The encoding of one band follows the generation of that band so that the band can be cleared from the memory after it has been encoded. This allows memory re-use, which is quite suitable for limited memory situations. However, in the implementation described in this dissertation, the running speed of the implementation has the highest priority when any trade-off needs to be made. Memory efficiency is considered when the implementation is designed but only because of hardware constraints. GPGPU computing model emphasizes on launching massive "workers" on the task to achieve high throughput. Even if each worker in GPGPU computing model has the same memory efficiency as the single worker in the sequential implementation, the overall memory usage of GPGPU computing model is still much higher than that of its CPU sequential counterpart because of the massive number of workers. In practice, a single worker of GPGPU implementation usually has less memory efficiency than its CPU counterpart because of GPU's memory fetching mechanism and synchronization limit, which will be explained in details in Section 2.2. Since the memory does not have the top priority during the implementation design in this dissertation, the forward encoding sequence becomes promising. The thumbnail image encoding can be achieved by forward encoding, with much less difficulties than backward encoding.

BCWT has made improvements over many existing wavelet-tree based algorithms by simplifying encoding mechanism, without decreasing compression efficiency [11]. However, BCWT needs further modifications on itself to be efficiently parallelized. Those modifications, which constitute PCWT, will be explained in details in Chapter 3 and 4.

## 2.2 General Purpose Graphic Processing Unit (GPGPU) Computing

General Purpose Graphic Processing Unit (GPGPU) Computing is to utilize the programmable graphics processing unit to perform general computing task, rather than its designated graphics related work.

GPGPU computing has two major models: Computation Unified Device Architecture (CUDA) and OpenCL. CUDA [18] is a proprietary model which is solely supported by Nvidia and OpenCL [19] is managed by Khronos Group which includes multiple vendors. However, CUDA has generally better supports than OpenCL, in terms of books, documentations and forums. In this dissertation, CUDA is chosen as the GPGPU computing model to implement PCWT.

CUDA includes a large range of topics and multiple books are even dedicated to CUDA itself. In this dissertation, CUDA is utilized but not the subject itself, so only directly relevant CUDA features are introduced in this section, which are CUDA memories, threads and synchronization.

### 2.2.1 CUDA Memories

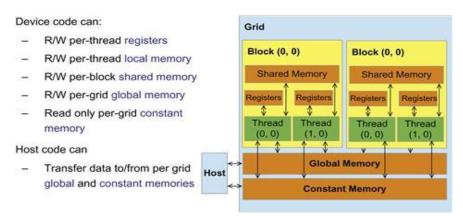

Figure 2.1 shows the memory structure of CUDA [20], which include multiple different types of memories: global memory, shared memory, constant memory, local memory, etc. Among them, global memory, shared memory and local memory are used in the PCWT implementation.

Figure 2.1 CUDA memory architecture [20]

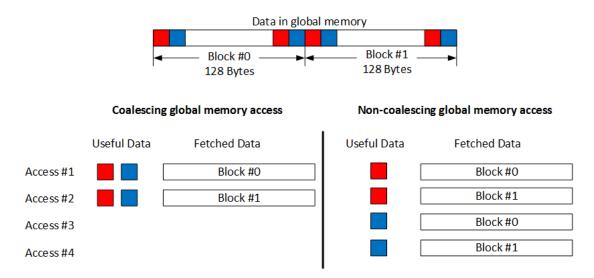

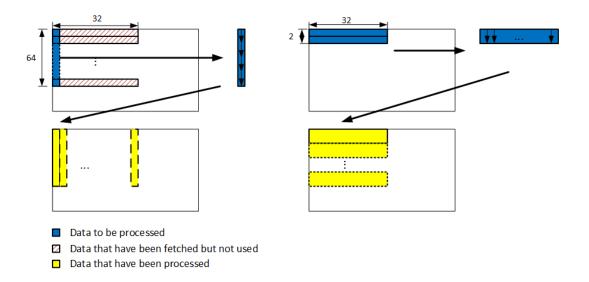

Global memory has the largest volume among all those three types of memories but the slowest access speed. The number of global memory accesses in any algorithm should be as few as possible. Furthermore, the access of global memory should be coalesced, which means multiple consecutive bytes should be accessed at the same time by algorithm. For CUDA computation capability 2.0 devices, in each global memory read/write, 128 bytes are accessed [21]. Figure 2.2 shows a comparison between coalescing and non-coalescing global memory access. Suppose one algorithm needs interlaced bytes from two 128-byte blocks at different places. If one implementation does not consider coalescing access and fetch the needed data only when the data is required, four memory reads are required. For each read, only 64 bytes out of fetched 128 bytes are actually used, however, totally 128 bytes are still fetched from global memory. On the other hand, if coalescing access is considered and all 256 bytes are pre-fetched by an implementation, only two global memory accesses, rather than four, are needed.

Figure 2.2 Comparison between coalescing and non-coalescing memory access of 256-byte data in the global memory

Shared memory is attached to each CUDA block and has less size than the global memory but higher access speed. CUDA block is a software term that will be explained with threads and synchronization. It can be understood as a working unit

with limited resources, e.g. limited shared memory attached to it. Different from global memory, shared memory does not require coalescing access. Shared memory is usually the place where intensive, random memory accesses happen. Note that shared memories belonging to different CUDA blocks are independent, meaning that "workers" in one block can only access to the shared memory of that block. "Workers" from one block cannot access the shared memory of another block. Shared memory will be further discussed with synchronization.

Local memory has the fastest access speed but highly limited volume. Each worker (i.e. thread) has its unique local memory. The limited volume of local memory usually constrains the use of it. For CUDA computation capability 2.0 devices, each worker has very limited local memory, i.e. only 63 32-bit registers and many of them are used by compiler without any notice to programmers. The available registers for programmers are much less than 63 and the exact number depends on how a specific program is compiled. Local memory should be used for distinguishing values of each thread, which are unique for each thread and need to be stored for further use. Use local memory to store input or output is neither efficient nor even possible in many cases.

## 2.2.2 Threads and Thread Divergence

After data is stored in memories of devices, "workers" are sent to process those data and generate the desired output. In CUDA, those workers are defined as threads. Threads are software abstract of working items supported by hardware, so it has both software and underlying hardware meanings. On hardware level, each thread represents a basic working unit in a CUDA core resident in a GPU multi-processor. One GPU card usually has multiple multi-processors. For example, Nvidia GTX 570 GPU has 15 multiprocessors, in each of which there are 32 CUDA cores (also called "wraps" in some CUDA literatures) and each CUDA core launches 32 threads at the same time. However, calculating the maximum parallel threads running at any given time by  $15 \times 32 \times 32 = 15360$  is not accurate, because not all 32 cores on one multiprocessor can run at the same time. CUDA hardware scheduling details are never

disclosed thoroughly, to the best of knowledge of the author. Based on some available materials [22], only a small number of 32 CUDA cores on each multi-processor can run at the same time. The reason why there are more CUDA cores existing than the number they can run simultaneously is that GPU can switch between CUDA cores when one specific core is idling for resources or data, e.g. waiting for a large amount of data read from memory.

In our implementation, the thread is more often referred as its meaning on software level. On software level, the whole task is divided into multiple CUDA blocks and in each block multiple threads execute their designated work independently. When all threads in one block finish their work, that block is done. When all blocks are done, the task is finished. In CUDA, each block has both thread and shared memory limits: for computation capability 2.0 device (e.g. GTX570), each block can launch at most 1024 threads, with 48kB shared memory. For example, if one block is used to process a 100x100 monochrome 32-bit image (i.e. single color per pixel and each pixel is 32-bit), data of that image can be copied to the block's shared memory and at most 1024 threads can be used to process all 10,000 pixels, which is about 10 pixels per thread.

The number of blocks used to process a specific task and the number of threads per block are determined by multiple factors, such as hardware constraints and algorithm design. In some cases, multiple blocks are mandatory. For example, if one image has large size, the shared memory of one block cannot hold the complete image and the whole processing has to be divided into multiple blocks. For 1000x1000 monochrome 32-bit images, the number of blocks should not be less than 976. In other cases, multiple blocks are the result of optimization. For example, multiple blocks are required if more threads are needed. To process the same 100x100 image to achieve higher processing speed, ten blocks with total 10,000 threads can be launched so that one thread in each block only needs to process one pixel. In practice, 10 times thread launching can achieve 2-5 times acceleration due to the fixed overhead of memory IO.

Note that CUDA threads are not completely independent. Each CUDA core launches 32 threads at the same time and those 32 threads are expected to do the same work at any given time. If any thread of those 32 threads performs different work from other threads, thread divergence happens. For example, if 32 threads of one CUDA core are used to process 32 elements (each thread for one element), even index threads (#0, #2, #4, ... #30) adds one to their corresponding elements and odd index threads (#1, #3, #5, ..., #31) subtracts one from their corresponding elements, thread divergence happens between even- and odd-index threads. To react to this divergence, CUDA runtime launches those 32 threads twice. In the first run, 32 threads are launched but only even-index threads do the real work i.e., adding one to elements, and odd-index threads are idling. In the second run, 32 threads are launched again, but only odd-index threads do the real work i.e. subtracting one from elements and even index ones are idling. It can be found that thread divergence affects the executing speed adversely. If all 32 threads perform adding or subtracting task, there is no thread divergence and only one run is needed. But with thread divergence, one extra run is needed. If the thread divergence is more severe, e.g. threads are sent to do 32 different tasks, the performance could be further degraded. Note that it is difficult to achieve zero thread divergence in most algorithm implementations but explicit thread index based branches, like the odd- and even-index thread example above, should be avoided whenever possible.

## 2.2.3 Synchronization

Blocks are not only used to provide parallel thread launching and fast shared memory, but they are also the synchronization basis of any task. Synchronization provides a deterministic state of execution of multi-thread tasks. Generally, the execution state of multi-thread task is undetermined. For example, if 128 threads are used to add one to each element of a 128-element array, thread #0 is not necessarily the first thread to start or finish. Thread #127 could be the first thread to launch due to the CUDA core scheduling. If the following execution depends on the completion of all 128 threads, synchronization is needed. Synchronization of all 128 threads means

the execution will halt until all 128 threads finish their work, so that the following execution can start without the risk that any thread within those 128 threads has not finished yet. However, only threads within the same blocks can be synchronized. For example, if 10 blocks with 1,000 threads in each block are used to process 10,000 pixels, only 1,000 threads within the same block can be synchronized. Thread #0 can be synchronized with thread #999 in the block #0; but thread #0 in block #0 cannot be synchronized with thread #0 in block #1. There is no guarantee that which block runs or finishes first after multiple blocks are launched (e.g. block #0 could run before block #1 and block #1 could run before block #0). This limited synchronization within the same block affects the design of algorithm, meaning tasks assigned to each block should not have any dependency on each other. Threads from different blocks can be synchronized only after one kernel is finished. Kernels can be viewed as parallel functions with block configuration attached to it. It can be understood as threads from different blocks can be synchronized only after all those blocks are finished. Kernel launching has its own overhead so launching too many kernels only for thread synchronization is not efficient. Parallelization of sequential algorithms is usually involved with execution flow change or even theoretical modification because of the limited synchronization of CUDA framework.

GPU memories and their accesses, thread launching, execution mechanisms and synchronization are the three main CUDA factors which affect re-design and implementation of the PCWT algorithm. These factors will be pointed out when the detailed implementation is explained in following chapters.

## **CHAPTER III**

## PCWT COMPRESSION PROCEDURE

The compression procedure includes six main stages: parallel Block-based Lifting-scheme Discrete Wavelet Transform with Boundary processing (B-LDWT+B), parallel MQD calculation, parallel QMAX search, parallel element encoding, parallel group encoding and sequential bitstream output.

### 3.1 Parallel B-LDWT+B

Parallel B-LDWT+B is to generate Lifting-scheme Discrete Wavelet Transform (LDWT) coefficients for following encoding stages. It is based on (5,3)-LDWT, with boundary processing and block configurations. Before explaining B-LDWT+B, the traditional (5,3)-LDWT is reviewed.

## 3.1.1 (5,3)-LDWT

For an array with 2N elements, 1D (5,3) forward LDWT can be calculated by [9]:

H-component (Odd-index elements):

$$D[2i + 1] = D[2i + 1] - [(D[2i] + D[2i + 2])/2]$$

,  $i = 0,..., N - 1$ . (Eq. 3-1)

L-component (Even-index elements):

$$D[2i] = D[2i] + [(D[2i-1] + D[2i+1] + 2)/4]$$

,  $i = 0, ..., N-1$ . (Eq. 3-2)

And the corresponding inverse 1D LDWT can be calculated by:

L-component (Even-index elements):

$$D[2i] = D[2i] - [(D[2i - 1] + D[2i + 1] + 2)/4]$$

,  $i = 0, ..., N - 1$ . (Eq. 3-3)

H-component (Odd-index elements):

$$D[2i + 1] = D[2i + 1] + [(D[2i] + D[2i + 2])/2]$$

,  $i = 0,..., N - 1$ . (Eq. 3-4).

The 2D (5,3) LDWT can be divided into two phases, i.e. 2D horizontal LDWT and 2D vertical LDWT, which are both depends on 1D (5,3) LDWT. Generally, 2D forward LDWT performs 2D forward horizontal LDWT first and 2D forward vertical

LDWT second. Correspondingly, the 2D inverse LDWT performs 2D inverse vertical LDWT first and 2D inverse vertical LDWT second.

Four implementation issues are needed to be addressed when implement 2D LDWT with CUDA:

- (1) 1D forward LDWT expects even number of working elements on each decomposition level. For N-level 2D forward LDWT, for the working matrix with size  $R \times C$ , one common step is to pad the row and column number of the working matrix to the smallest power of 2 integer  $(2^N)$  that is not less than R and C. However, this type of padding causes unnecessary computation. For example, to perform 2-level 2D forward LDWT on matrix 129x129, the matrix is padded to 256x256. Only about 25% elements are effective elements.

- (2) When (5,3)-LDWT is performed on an array with finite 2N elements D[j] (j = 0, ..., 2N 1), two elements D[2N] and D[-1] do not exist, when compute H-components and L-components, respectively.

- (3) CUDA can only provide limited shared memory for either horizontal or vertical (5,3)-LDWT. For Computation Capability 2.0 devices, the shared memory limit for each block is 48kB. Using shared memory is critical for obtaining the correct forward LDWT or inverse LDWT result fast. Shared memory allows much faster memory access than the global memory and synchronization of threads from the same block. Synchronization ensures that H- and L-component computations are performed deterministically and guarantees the correctness of the generated result.

If a specific GPU hardware does not have enough shared memory to process a complete row or column of 2D (5,3)-LDWT, without proper modifications, the direct block-wise LDWT implementation introduces block effects on the boundary of each block [15].

(4) Forward (5,3)-LDWT generates interlaced decomposition results in which L-components are interlaced with H-components. In practice, generated L- and H-

components are expected to be clustered as the intermediate result for the next level decomposition or as the final result to be presented.

To solve the issues mentioned above, Block-wise LDWT with Boundary processing (B-LDWT+B) is proposed to perform fast and efficient LDWT without loss and block effect.

### 3.1.2 Parallel B-LDWT+B

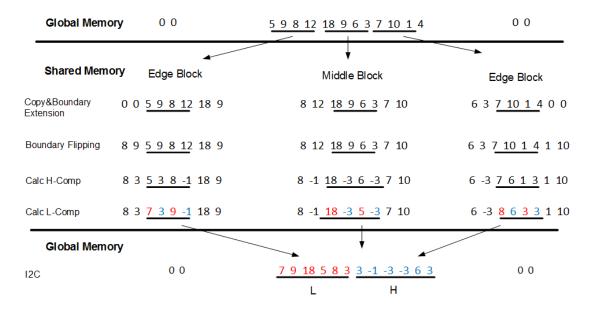

Figure 3.1 shows an example of forward 1D B-LDWT+B transform with boundary processing and I2C operation, on a 12 elements with 3 blocks. The rest of this section will explain how steps in 1D B-LDWT+B are introduced to solve the issue (1) to (4) mentioned in the last section (Section 3.1.1).

Figure 3.1 Forward 1D B-LDWT+B transform on 12 elements with 3 blocks

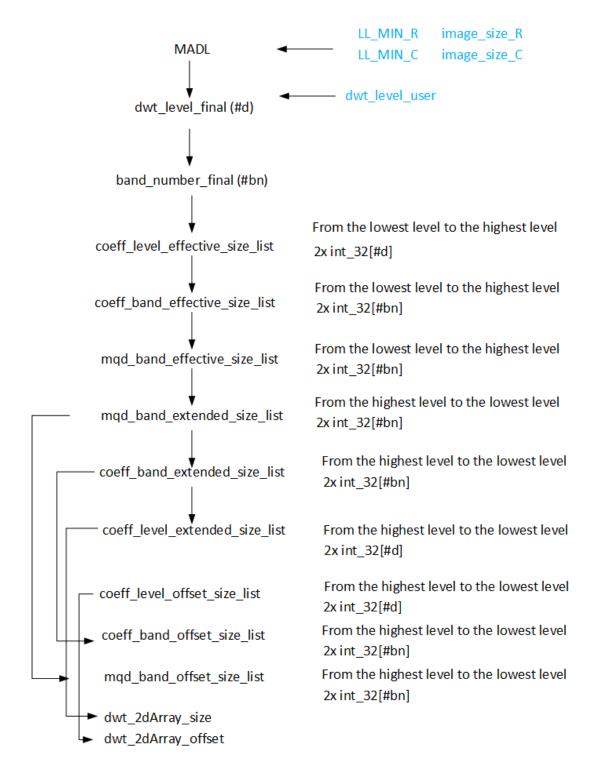

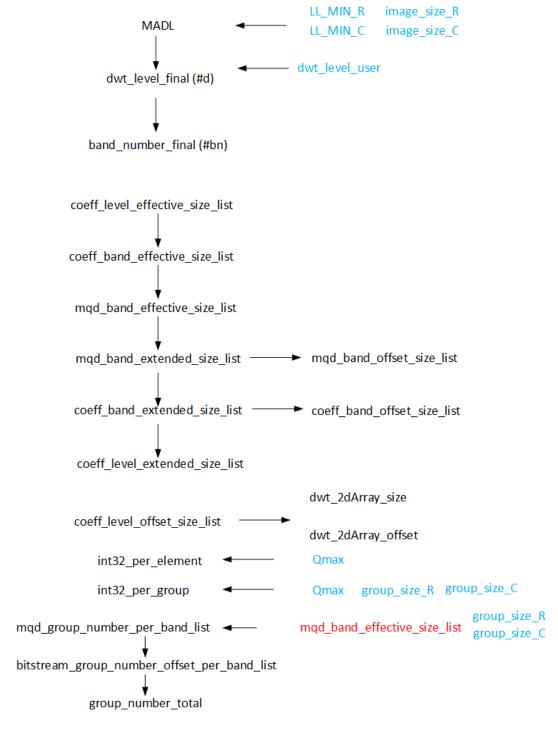

To solve issue (1), the Maximum Allowed Decomposition Level (MADL) of 2D forward LDWT and band/level size list are proposed.

Theoretically, with proper padding, 2D forward LDWT can be performed continuously until 1x1 LL band is achieved. However, more levels 2D forward LDWT performs with, smaller sizes of top level bands are generated. Lacking of enough elements in those bands limits the parallelism of computation of those bands. The

limited benefits from parallelism of small highest level bands can be overwhelmed by cost of transforming data between host (CPU) and device (GPU) in terms of running time, which means small sizes of top bands affect the performance of our parallel algorithm adversely. The MADL is proposed to constrain the level used for 2D forward LDWT, based on the size of working matrix. It means matrices with different sizes have different MADLs.

The MADL can be calculated based on the pre-set minimum row and column number of the highest level band size LL\_MIN\_R and LL\_MIN\_C. For example, if LL\_MIN\_R is set to 64, which means the row number of LL band should be equal or larger than 64. For images with size  $1024 \times 1024$ , the maximum allowed decomposition level of DWT is 4, because  $\frac{1024}{2^4} = 64$  but  $\frac{1024}{2^5} = 32 < 64$ .

The MADL aims at improving performance of B-LDWT+B implementation, but it also helps the implementation to avoid over-computation by not performing unnecessary decompositions that is above MADL.

Note that over-computation still exists in decompositions within MADL, and level/band size is proposed to handle that. "Level size" is defined as the row number and column number the input matrix for one level 2D LDWT. "Band size" is defined as the row number and column number of bands generated by 2D LDWT. In standard 2D LDWT implementation, the level size and band size are "interchangeable", which are only different with a factor of 2. However, in our algorithm, level sizes and band sizes are relative but calculated differently. Level sizes are used in both forward and inverse LDWT and band sizes are mainly used for encoding (i.e. band-based encoding) and decoding.

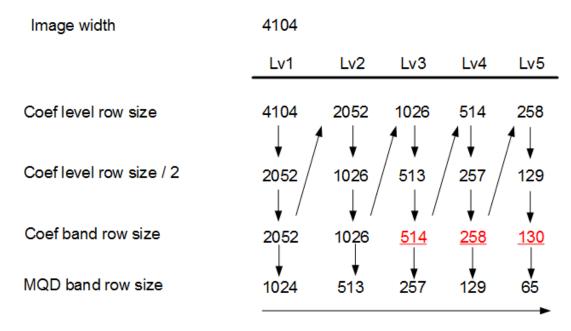

Figure 3.2 Band and level size calculation

Figure 3.2 shows an example of difference between level size and band size.

Differences rise from different rules on which level sizes and band sizes are calculated.

For level size, the level size of any level must be even. In Figure 3.2, the level row size at Lv4 would be 513 if directly calculated from Lv3 ( $\frac{1026}{2}$  = 513). The actual level size at Lv4 is padded to 514 with one row of 0, to ensure the Lv4 LDWT decomposition can be done. However, the level row size at Lv3 is still maintained as 1026 rather than 1028 (2 × 514 = 1028). The potential over-computing of forward DWT on Lv3 is avoided.

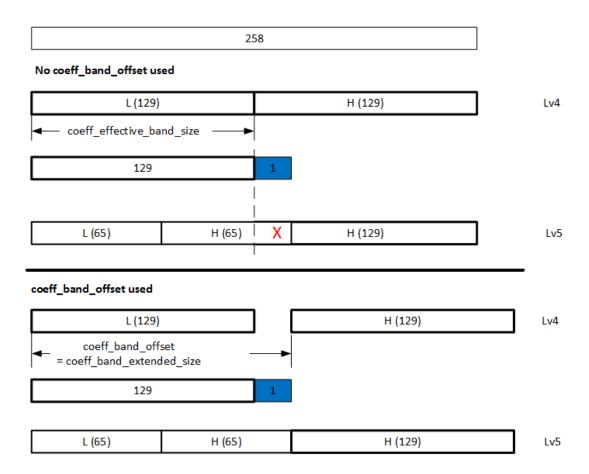

On the other hand, for band size, the band size of any band must be even. This is from the assumption of following encoding stages, which is "every band should have corresponding MQD band". In Figure 3.2, the band's row size at Lv5 would be  $129 \left(\frac{258}{2} = 129\right)$  but is padded to 130. However, the band's row size at Lv4 is still 258 rather than  $260 \left(2 \times 130 = 260\right)$  so the potential over-computing and further overencoding in following encoding stages on Lv4 is avoided.

There is another parameter related with level and band size, i.e. the band offset. It will be explained in Section 4.4.

To address issue (2), boundary processing is needed to substitute the missing element D[2N] and D[-1] in the data array. In B-LDWT+B, two types of boundary processing methods, boundary flipping and boundary extension, are used. Choosing these methods instead of using simple padding zero or mirroring boundary is because of the block constraints in solution of issue (3). The details of boundary flipping and boundary extension will be explained when addressing the issue (3).

To address the issue (3), both horizontal 2D B-LDWT+B and vertical 2D B-LDWT+B have to be processed block by block. Blocks here refer to CUDA blocks but they can be conceptual blocks of image processing fields. Directly dividing the input 2D matrix into multiple blocks and processing those blocks independently without proper boundary processing brings the boundary effect to the DWT decomposition result. Such rough block division will also cause the "fixed block size" problem that is the block size used in forward transform could hinder the execution of inverse transform. For example, if the hardware used in forward transform has enough memory to process blocks with size 512x512 but the hardware used in inverse transform does not have enough memory to process the same size blocks, the lossless inverse transform is not able to proceed.

Boundary flipping and boundary extension are used in B-LDWT+B to achieve block-wise lossless LDWT with arbitrary block configuration. As shown in Figure 3.1, blocks in our B-LDWT+B implementation can be classified into two categories: edge blocks and middle blocks. For edge blocks, boundary-flipping (mirroring the boundary elements) is used on one end and boundary extension (reading elements outside the current block) is used on the other end. For middle blocks, boundary extensions are used on both ends. Figure 3.1 shows an example of boundary flipping and boundary extension of edge and middle blocks.

To solve the issue (4), embedded Interlacing-to-Clustering (I2C) operation is introduced to cluster the L- and H-components. "Embedded" means this operation is embedded in both L- and H-component calculation so that there is no extra clustering step after L- and H-component calculations are finished. As shown in Figure 3.1, the clustered result (L-components are marked in red and H-components are marked in blue) is stored in the global memory as the result of 1D B-LDWT+B, without an extra clustering operation involved.

Comparing to the alternative independent I2C operation, there are several advantages of embedded I2C operation:

- (1) The kernel launching overhead [23] of extra I2C operation can be avoided;

- (2) Implementation of embedded I2C operation is simpler than independent I2C operation. Each embedded I2C operation is performed in either horizontal or vertical direction, which means it needs to handle only two types of components, i.e. L-components and H-components. The independent I2C operation clusters elements in both horizontal and vertical direction, so it has to process four types of components, i.e. LL-, HL-, LH- and HH-components;

- (3) The number of global memory operations of the embedded I2C operation is less than those of independent I2C operation. Independent I2C operation needs extra global memory access to read the interlaced result into shared memory, process it and write the clustered result back to global memory. Those extra global memory accesses will decrease the overall running speed of B-LDWT+B.

2D B-LDWT+B is a variant of (5,3)-LDWT, with boundary processing, block configurations and embedded clustering operations. Different from traditional CPU-based 2D (5,3)-LDWT, in which identical 1D LDWTs are performed on different directions i.e. horizontal and vertical directions sequentially, implementations of horizontal and vertical part of 2D B-LDWT+B has significant differences. Section 3.1.3 and 3.1.4 will describe the details of horizontal and vertical part of 2D B-LDWT+B and demonstrate those differences.

## 3.1.3 Implementation of Horizontal 2D B-LDWT+B

Horizontal 2D B-LDWT+B includes six steps:

- (1) The input matrix, i.e. the original image for the first level decomposition or the LL band from the previous decomposition, is divided into blocks. One block contains a part of row. For input matrix size  $R \times C$ , the block configuration is  $R \times \left[\frac{C}{b}\right]$ , in which b is the number of element processed by one block.

- (2) Blocks are read from GPU global memory (global memory 2D array #1) into blocks' corresponding shared memories. For each block, four extra elements outside the block are also read for boundary extension, as shown in Figure 3.1. The elements designated to be processed by the block are called effective elements and the 4 extra elements are called boundary elements. Effective elements and boundary elements constitute the input section of shared memory of that block.

- (3) Optional boundary flipping is performed on one end of the input section, if the block is a boundary block.

- (4) Calculate H-components.

- (5) Calculate L-components. Note the interlaced result is generated after this step and generated H- and L-components are stored in the output section of shared memory.

- (6) Perform embedded I2C operations on generated H-elements and L-elements. The interlaced result is copied from 2D array #1 to another global memory 2D array (2D array #2). Extended band offsets, which will be explained in section 4.4, are used to relocate H- and L-elements in 2D array #2.

Note that there are cases that the rightmost blocks has fewer elements than the preset block size. For example, if the width of image is 640 and the block size is 256, then each row is divided into 3 blocks, with 256, 256, and 128 elements, respectively. With proper boundary processing, i.e. boundary extension on the left end and boundary flipping on the right end, those rightmost blocks can proceed through step

(2) to (6) without any padding. It means that the rightmost block with 128 elements does not have to be padded to 256 elements.

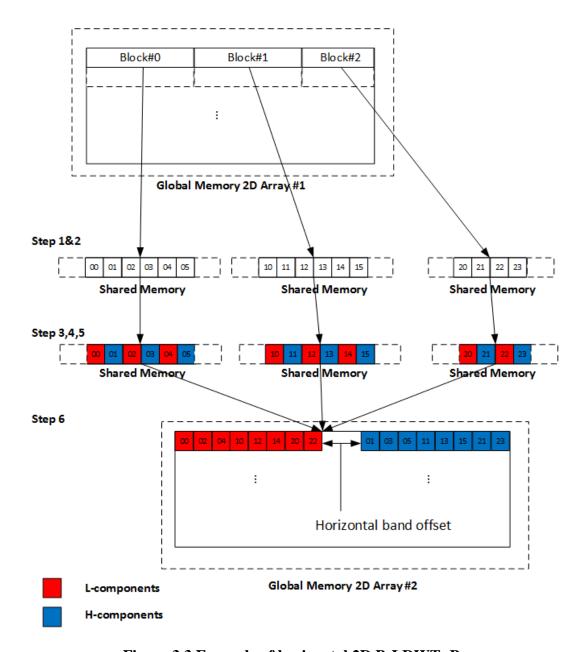

Figure 3.3 shows an example of horizontal 2D B-LDWT+B. Each row of the input matrix in global memory 2D array #1 has been divided into three blocks. Block #0 and #1 are complete block and block #2 is the incomplete block which has fewer elements than block #0 and #1. After step 1 and 2, each block has been read into shared memory, with boundary extension that is marked by broken lines. After step 3, 4 and 5, the L- and H-components in each block has been generated. After step 6, clustered L- and H-components are stored in global memory 2D array #2. Note there is a horizontal band offset between generated L and H bands, which will be explained in section 4.4.

Figure 3.3 Example of horizontal 2D B-LDWT+B

## 3.1.4 Implementation of Vertical 2D B-LDWT+B

Vertical 2D B-LDWT+B has different implantation from its horizontal counterpart because of the 2D array storage mechanism in GPU global memory and global memory coalescing access. The 2D array is stored row by row in GPU's global memory and 2D array can be only accessed efficiently in a coalescing pattern which

requires threads in one CUDA block to read consecutive global memory (generally 128 bytes [21]).

The efficient way to access elements in 2D array in global memory is to read elements row by row, and the direct access a single column of 2D array is not efficient. Figure 3.4 shows the comparison between column-wise and row-wise 2D matrix processing. Assume element processing in both methods are the same so that the difference is majorly introduced by the coalescing global memory access. To process the input matrix with size 64x32, each fetch of column-wise processing reads a complete column by using 64 memory accesses and most of elements read are dropped. Overall, column-wise 2D matrix processing performs 2048 global memory accesses. On the other hand, the row-wise processing fetches the data by coalescing accesses. Suppose each fetch only reads two rows, i.e. 64 elements which fit the number of elements processed in column-wise processing. Overall, row-wise 2D matrix processing performs only 64 global memory accesses. It can be found that by using row-wise 2D matrix processing method, temporal cost of data I/O, which is notorious performance bottleneck of GPGPU computing [24], is decreased to 1/32. Nevertheless, in some cases, row-wise 2D matrix processing method requires modifications on algorithms to accommodate the data structure fetched into the processing unit, especially when the original algorithm is column-wised, like vertical 2D B-LDWT+B.

Figure 3.4 Comparison between column-wise and row-wise 2D matrix processing

To increase the efficiency of global memory access in vertical 2D B-LDWT+B, the block used in vertical 2D B-LDWT+B is 2D, which means each block includes elements from multiple rows and columns.

Vertical 2D B-LDWT+B includes six steps:

- (1) The input matrix, i.e. the result of the previous horizontal 2D B-LDWT+B, is divided into multiple blocks. One block contains multiple partial columns. For input matrix size  $R \times C$ , the block configuration is  $\left\lceil \frac{R}{r} \right\rceil \times \left\lceil \frac{C}{c} \right\rceil$ , in which r and c are the number of elements processed by one block in horizontal and vertical direction, respectively.

- (2) Similar to horizontal 2D B-LDWT+B, blocks are read from GPU global memory (global 2D array #2) into the blocks' corresponding shared memory. For each block, four extra rows of elements outside the block are also read for boundary extension.

- (3) Optional boundary flipping is performed if the block is boundary block.

- (4) Perform H-step of 1D B-LDWT+B.

- (5) Perform L-step of 1D B-LDWT+B.

(6) Perform embedded I2C operations on generated H-elements and L-elements. The interlaced result in global 2D array #2 is clustered and copied to global 2D array #1. The clustered result in 2D array #1 can be used for the next level decomposition or output of the whole 2D B-LDWT+B stage.

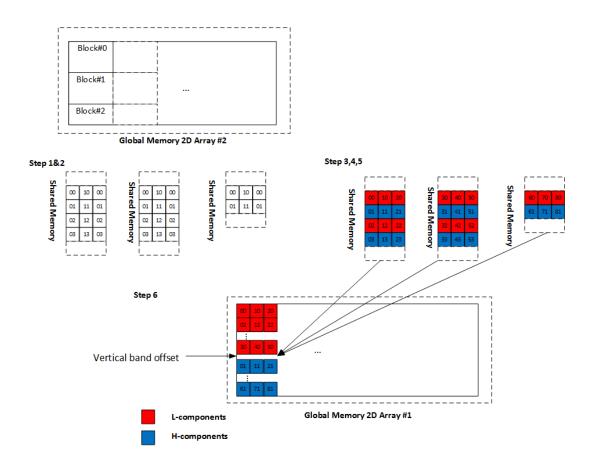

Figure 3.5 shows an example of vertical 2D B-LDWT+B. The result of horizontal 2D B-LDWT+B has been stored in global memory 2D array #2. Each 2D block contains 4x3 elements. The row number is larger than the column number for each 2D block reflects that in each block transform is performed along each column. Each block should contain as many elements in vertical direction as possible. Similar to the example in Figure 3.3, Block #0 and #1 are complete block and block #2 is the incomplete block which has fewer elements than block #0 and #1. After step 1 and 2, each block has been read into shared memory, with boundary extension that is marked by broken lines. After step 3, 4 and 5, the L- and H-components in each block have been generated. After step 6, clustered L- and H-components are stored in global memory 2D array #1. Note there is also a vertical band offset between generated L and H bands, which will be explained in section 4.4.

Figure 3.5 Example of vertical 2D B-LDWT+B

Note that in the previous horizontal 2D B-LDWT+B, the block could be also set as 2D. Processing one partial row in 2D horizontal B-LDWT+B needs extra elements i.e. boundary elements, which usually causes extra global memory accesses. To decrease the temporal cost from those extra global memory accesses, each row should be divided into as few partial rows as possible. Since each block's shared memory is limited, in 2D horizontal B-LDWT+B, the block is chosen as 1D, which requires less block number for each row than 2D block.

Similarly, in vertical 2D B-LDWT+B, block number that is used to process each column is expected as little as possible. However, the block's height cannot be arbitrarily large because of limited block shared memory and 128 bytes (thrity-two 32-bit integers) recommended block row width.

#### 3.2 Parallel MQD calculation

#### 3.2.1 Modified MQD calculation

There are multiple methods to encode the generated 2D B-LDWT+B coefficients. In our algorithm, Maximum Quantization Descent (MQD) is used to encode coefficients because of its inherited parallelism. In general, every four coefficients with their corresponding MQDs can be encoded independently.

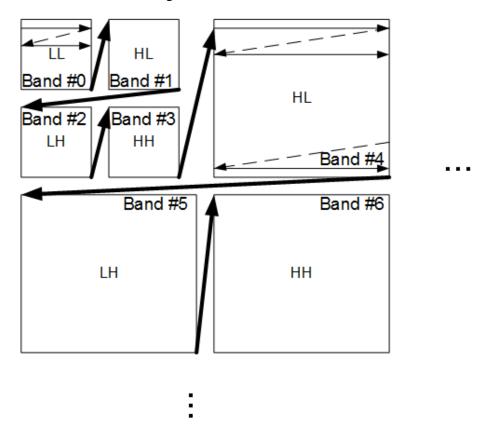

Different from the original BCWT [11], in our algorithm, all coefficient bands have their corresponding MQD matrix, called MQD bands. It means that all HL, LH, HH and LL (only exists on the top level) bands have their corresponding MQD bands. This simplifies the encoding procedure and decreases the difficulties in implementing our algorithm.

The generation of MQD matrix is from the lowest level to the highest level. There are two types of MQD bands:

- (1) MQD band without corresponding lower level MQD band's support and

- (2) MQD band with corresponding lower level MQD band's support.

Type (1) MQD bands are MQD bands corresponding to coefficient bands on the lowest level and the LL band. Type (2) bands are MQD bands corresponding to the remaining coefficient bands. Two types of bands have different calculation rules: For type (1) MQD band, only coefficients are involved in the calculation. More specially, for each MQD element in type (1) MQD band, only 4 coefficients are used. For type (2) MQD band, both coefficients and MQD elements from supportive MQD bands are involved. It means that for each MQD element in type (2) MQD band, 4 coefficients from its corresponding coefficient band and 4 MQD elements from its supportive MQD band are used.

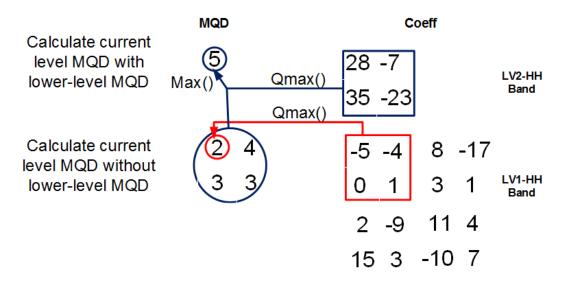

Figure 3.6 shows MQD calculation with and without lower-level MQD band on Lv2 and Lv1, respectively. "Qmax()" is a function used to find the maximum Quantization Level (QL) of current level four-coefficient unit [11]. The QL of one coefficient can be understood as the minimum number of bits that are needed to

losslessly store the absolute value of that coefficient. However, there are differences between QL of one coefficient and actual minimum number of bits needed by the coefficient. QL = 0 means the minimum number of bits is 1 bit. And the 0's QL is defined as -1. "Max()" is a function used to find the maximum value among a group of numbers.

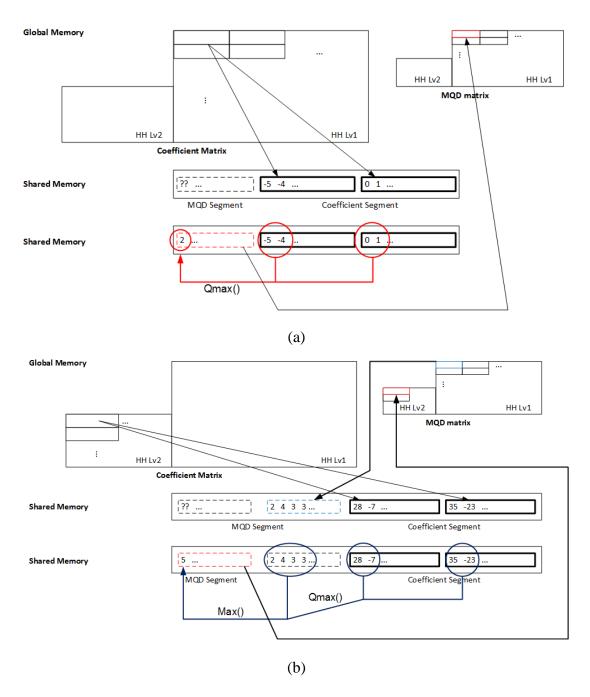

Figure 3.6 Calculation of two types of MQD bands

To calculate type (1) MQD, for example, to calculate four coefficients (-5, -4, 0, 1)'s MQD, QL of each coefficient is calculated first:

$$QL(-5) = \lfloor \log_2(|-5|) \rfloor = 2,$$

$QL(-4) = \lfloor \log_2(|-4|) \rfloor = 2,$

$QL(0) \stackrel{\text{def}}{=} -1,$

$QL(1) = \lfloor \log_2(|1|) \rfloor = 0.$

The maximum QL out of those four QLs is 2, which means the MQD of those four coefficients is 2.

To calculate type (2) MQD, for example, the MQD of four coefficients (28, -7, 35, -23), QL of each coefficient is calculated first:

$$MQL(28) = \lfloor \log_2(|28|) \rfloor = 5,$$

$$MQL(-7) = [Log_2(|-7|)] = 2,$$

$$MQL(35) = [Log_2(|35|)] = 5,$$

$$MQL(-23) = \lfloor Log_2(|-23|) \rfloor = 4,$$

Note the candidate MQD, but not the final MQD, is 5.

Then four MQDs from the supportive MQD band are obtained as (2, 4, 3, 3) and the maximum value among those four MQDs and the candidate MQD is 5. The final MQD is determined as 5.

# 3.2.2 Implementation of Parallel MQD Calculation

In parallel MQD calculation, each MQD band is divided into multiple blocks. Currently, there is no parallelism between bands, which means one CUDA kernel processes one band and bands of MQD matrix are processed sequentially. Parallelism can be expended from within-band to between-band. To process multiple bands in one CUDA kernel, different band offsets need to be sent to the kernel and branches for different bands are introduced into the kernel, which could degrade the performance of parallel MQD calculation.

The processing sequence of bands is from the lowest level to the highest level. Within each level, it follows HL-, LH- and HH-band sequence. The last band to be processed is the LL band.

The parallel MQD calculation for one band includes four steps:

- (1) The MQD band is divided into multiple blocks. For the target MQD band with size  $R \times C$ , the block configuration is  $R \times \left[\frac{C}{N}\right]$ , in which N is the number of MQDs generated by each block.

- (2) For type (1) MQD band, each block takes  $2 \times 2N$  coefficients from the current level coefficient band in the global memory. For type (2) MQD band, each

block takes  $2 \times 2N$  coefficients from the current level coefficient band and  $1 \times N$  MQDs matrix from the supportive MQD band in the global memory.

- (3) Each thread generates one MQD, called the target MQD. The target MQD is generated from four coefficients, with or without four supportive MQDs. The thread obtains the maximum coefficient of these four coefficients and calculates its QL. If the band is type (1), the calculated QL is the target MQD; if the band is type (2), the calculated QL is taken as the candidate MQD and compared with four supportive MQDs. The maximum value among them is taken as the target MQD.

- (4) After all  $1 \times N$  MQDs of one block are generated, the block copies those MQDs back to MQD matrix in global memory, based on the offset and size of the band. The calculation of each MQD band's offset and size will be demonstrated in section 4.4.

Figure 3.7 shows an example of parallel MQD calculation. It is based on the same numerical example in Figure 3.5. It can be found that the processing band has been divided into blocks. As shown in Figure 3.7 (a), for type (1) MQD band, only coefficients are read into the shared memory and calculated MQD is copied back to corresponding MQD band. For type (2) MQD band, as shown in Figure 3.6 (b), both coefficients and MQDs from supportive MQD band are copied into the shared memory. Note the distance between coefficients from two rows, for example, the offset between coefficients -5, -4 and 0, 1 in Figure 3.6 (a), which reflects the rowwise storage in the shared memory.

Figure 3.7 Example of parallel MQD calculation

#### 3.3 Parallel Qmax search

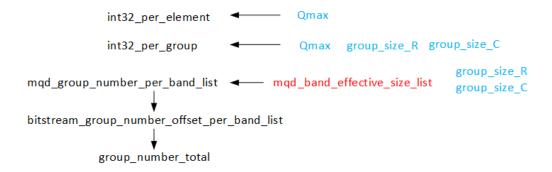

## 3.3.1 Qmax and parallel maximum value search

Qmax is defined as the maximum value within the highest level of MQD matrix, called "search matrix". The search matrix includes MQD bands corresponding to LL-, HL-, LH- and HH-band on the highest level of coefficient matrix. Qmax is used to encode the highest level MQD bands, which will be explained in section 3.4.

The temporal complexity of sequential comparison-based maximum value search is at least O(n), which means it is linearly proportional to the amount of data to be processed. "Comparison-based" means that the maximum value is obtained as the result of a series of comparisons. If any new value is larger than the current maximum value, the maximum value is updated with the new value; otherwise the maximum value remains unchanged. O(n) reflects the fact that it is impossible to tell the maximum value of a list without at least checking each element in the list. Parallel Qmax search utilizes more hardware resources, i.e. more threads on more data within a given time internal, to decrease the overall temporal complexity of search.

Maximum value search is parallelizable to a certain degree. The parallel maximum value search used in PCWT is a comparison-based reduction operation on the search matrix. "Reduction" means the number of elements being operated decrease gradually along with the proceeding of search.

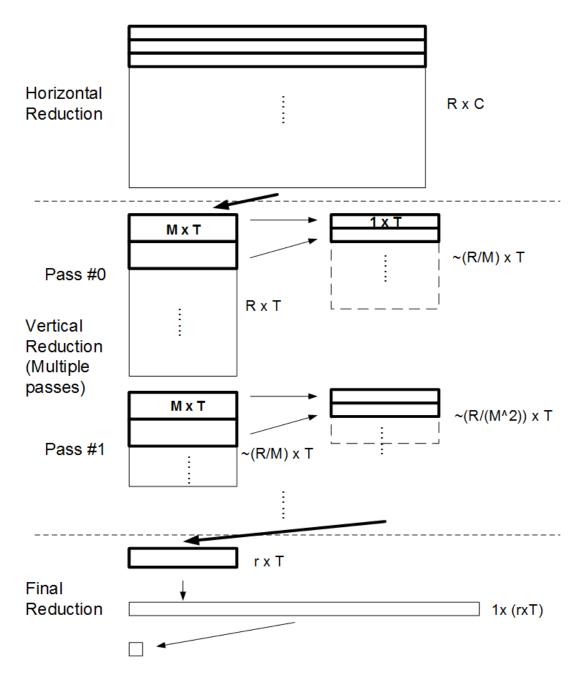

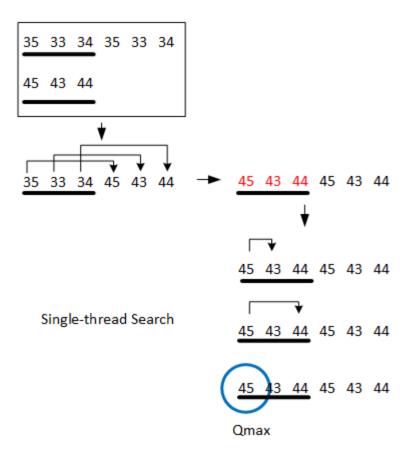

As shown in Figure 3.8, there are three phases in Qmax parallel search: horizontal reduction, vertical reduction and final reduction. Their implementation details will be explained in following sections 3.3.2 to 3.3.4.

Figure 3.8 Three main phases of parallel Qmax search

# 3.3.2 Implementation of horizontal reduction

Horizontal reduction is a block-based parallel operation to reduce the horizontal dimension of the search matrix, i.e. the number of columns in the search matrix. Each block processes one row of search matrix, which implies that the shared

memory of one block can hold a complete row of the search matrix. For CUDA, this assumption is reasonable. Use 10000x10000 images as an example, after 5-level B-LDWT+B is performed, the width of search matrix is less than 256. The typical size of CUDA shared memory per block is 48kB which can hold more than 10,000 32-bit integers. Therefore, the assumption is valid for most of images. The horizontal reduction having multiple blocks for one row can be implemented in a multi-pass style that is similar to the following vertical reduction, which will be described in details in section 3.3.3.

The horizontal reduction has four steps:

- (1) The search matrix is divided into multiple blocks. For the search matrix with size  $R \times C$ , the block configuration is  $R \times 1$  and each block processes C elements.

- (2) Each block copies one row from the original search matrix into the block's shared memory.

- (3) In each block, T threads are launched and thread t performs comparison-based maximum value search on element t, 2t, 3t until the end of row. The element t, 2t, 3t, ... are called the thread t's search range within the block. The maximum value within that search range is updated at element t, meaning that the current maximum value is always stored at element t.

- (4) Copy the reduced row with size T, which consists of maximum values from each thread's search range, back to the original search matrix. Note that the horizontal reduction generates a horizontally compacted search matrix with size  $R \times T$ .

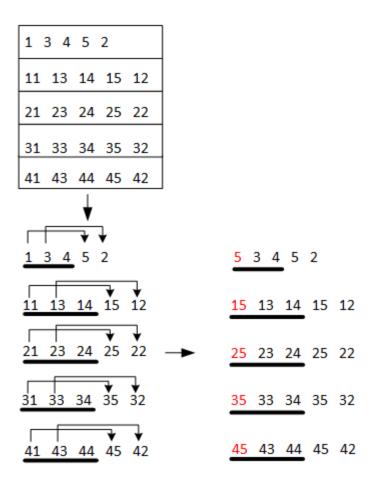

Figure 3.9 shows an example of horizontal reduction on a 5x5 search matrix. Suppose each block can hold maximum 6 elements and T = 3. It means that three threads are used in each block.

Figure 3.9 An example of horizontal reduction

Each row of the search matrix is assigned to a block and each thread compares the first element with the rest elements in its search range. Note that the third thread in each block has only one element in its search range, for example, 4 in the first row or 14 in the second row.

The maximum value within each thread's search range replaces the first element in its search range. For example, for the first thread in the first block, element 5 replaces element 1. But for the second thread in the same block, the first element 3 is the larger than element 2, so that there is no update.

The resulting 5x3 matrix (whose elements are marked by blank underscore lines) is the generated horizontally compacted matrix, which is the input for the next phase.

## 3.3.3 Implementation of vertical reduction

After the horizontal reduction is finished, the vertical reduction is performed to reduce the vertical dimension of the search matrix i.e. the row number of the search matrix. The goal of vertical reduction is to reduce the number of horizontally compacted rows, so that the final reduction, which will be explained in section 3.3.4, can use only one block to process all remained rows and obtain the final maximum value. The vertical reduction is a block-based multi-pass parallel operation. "block-based" means in each pass, the working matrix is divided into multiple blocks. Each block reduces multiple rows into one row to achieve in-block vertical reduction. "Multi-pass" indicates that in many cases, one pass cannot reduce the number of elements in the resulting matrix below the maximum allowable size of final reduction, so the vertical reduction needs multiple passes to achieve its goal.

In general, if one pass in the vertical reduction can approximately reduce the vertical size of the working matrix to  $\frac{1}{M}$ , the number of passes P to reduce the matrix row number from R to r can be calculated as:  $\frac{R}{M^P} = r$ , that is  $P = log_M \frac{R}{r}$ . It is an efficient reduction, for example, if the vertical size needs to be decreased from R = 10000 to r = 10 and each block can contain M = 10 rows, only three passes are required.

The vertical reduction includes multiple passes. In each pass, the vertical reduction has four steps:

- (1) The current working matrix is divided into multiple blocks. For the matrix with size  $R \times T$ , the block configuration is  $\left\lceil \frac{R}{M} \right\rceil \times 1$ , in which M is the number of rows per block. Note that after each pass, the row number of the current working matrix decreases.

- (2) Each block copies M rows from the working matrix into the block's shared memory. These M rows merge into a 1D search array with the size TM.

- (3) In each block, T threads are launched and thread t performs comparison-based maximum value search on element t, t, t until the end of row. Similarly to the horizontal reduction, the element t, t, t, t, are called the thread t's search range within the block. The maximum value within that search range is updated at element t.

- (4) Copy the search results (the first *T* elements of the 1D search array) back to the current search matrix.

After each pass, the current working matrix shrinks from  $R \times T$  to  $\left\lceil \frac{R}{M} \right\rceil \times T$ . If  $\left\lceil \frac{R}{M} \right\rceil < r$ , in which r is the pre-set maximum number of rows processed in the final reduction, the vertical reduction stops; otherwise, another pass starts.

Figure 3.9 shows a follow-up example based on the result in Figure 3.8. Each block contains two horizontally compacted rows so the 5x3 matrix is divided into three blocks. In each block, a comparison-based maximum search, which is similar to the one in horizontal reduction, launches. After the 1<sup>st</sup> pass, a 3x3 vertically reduced matrix (whose elements are marked by blank underscore lines) is generated. It still contains 9 elements, which exceeds the maximum allowed number of elements per block i.e. 6. After the 2<sup>nd</sup> pass, a 2x3 vertically reduced matrix (whose elements are marked by blank underscore lines) is generated. It can fit into a single block and vertical reduction stops.

Figure 3.10 Example of vertical reduction

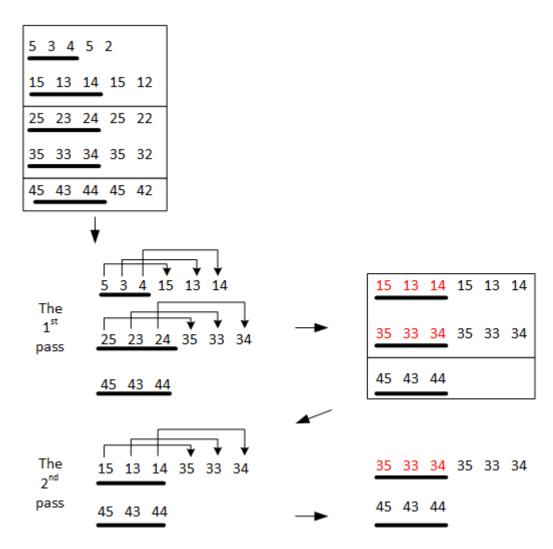

## 3.3.4 Implementation of final reduction

After the vertical reduction, the size of search matrix has been decreased so that the remained search matrix can fit into a single block's block memory. The final reduction is a single-block, multi-thread operation to find the maximum value of the whole MQD matrix.

The final reduction can be viewed as a variant of vertical reduction. It includes four steps:

- (1) Only one block is used. Copy the result of vertical reduction to the block's shared memory row by row and form a concatenated row.

- (2) Similarly to the vertical reduction, T threads are launched and thread t performs comparison-based maximum value search on element t, 2t, 3t until the end of row. This step reduces the concatenated row to a compacted row with size T.

- (3) One thread (usually the thread t = 0) performs comparison-based maximum value search on the compacted row from step (2) and the global maximum value is stored at the first element of the compacted row.

- (4) Copy the final result back to the global matrix.

Figure 3.11 shows an example of final reduction based on the result in Figure 3.10. One block is used to process the remained 2x3 matrix. First, three threads are used to find and relocate maximum values within their search range. Second, one single thread is used to search through three remained maximum values. The final maximum value i.e. 45, is found as the result of the single-thread search.

It can found that most parts of parallel Qmax search are multi-block, multi-thread operations, which have high parallelism. The only single-block, multi-thread operation is the final reduction and the only single-thread operation is the step (3) in the final reduction. This parallelism decrease trend reflects the intrinsic of reduction operation, in which number of elements being operated are decreasing gradually. The influence of lacking of parallelism in the final phase of the maximum MQD search is neglectable. For example, for an MQD with 256x256, if 32 threads per block are used to process them, in the final stage, there are only 32 elements left for step (3), which means less than 0.1% MQDs are operated by a single thread.

Figure 3.11 Example of final reduction

## 3.4 Parallel Element Encoding

#### 3.4.1 Elements in Parallel Element Encoding

Parallel element encoding is to encode the generated B-LDWT+B coefficient to bitstream. This stage is the core stage of the whole algorithm. "Element" in parallel element encoding refers to the basic unit of encoding, which includes one MQD and four corresponding coefficients in one band at one level. In Figure 3.6, one element is (5; 28, -7, 35, -23) and another element is (2; -5, -4, 0, 1).

The procedure of encoding elements is similar to the procedure of calculation MQD. In BCWT, they are combined so that high memory efficiency can be achieved. However, those two procedures are separated in PCWT, because of the limited resources available in CUDA. As shown in previous sections, most of stages in PCWT

are implemented in the unit of block. Because of limited resources of each block (e.g. limited shared memory, limited number of threads, etc.), a common trade-off is between number of threads that can be launched per block and complexity of task performed by each thread. If element encoding is combined to MQD calculation, one obvious consequence is the high data demand from each thread, in which data required by element encoding and data required by MQD calculation merge. Data from three levels i.e. the current level, the neighboring higher level, and the neighboring lower level, are involved in element-encoding-MQD-calculation-combined operation, which would causes fewer available threads than separated element encoding or MQD calculation operation. Operations in the current separated MQD calculation and element encoding stage need data only from two levels. In PCWT, the complexity of task is decreased to allow more parallelism. Besides that, the forward encoding sequence is an important reason to separate MQD calculation stage from element encoding stage.

## 3.4.2 Element Encoding Sequence and Rules

Figure 3.12 shows the encoding sequence of element encoding.

The parallel element encoding stage has the following encoding sequence:

- (1) The level encoding sequence is from the highest level to the lowest level.

- (2) For the highest level, the band encoding sequence is top-left, top-right, bottom-left and bottom-right, i.e. LL band, HL band, LH band and HH band. For the rest of levels, the sequence is top-right, bottom-left and bottom-right, i.e. HL band, LH band and HH band.

- (3) Within a band, elements are encoded row by row from top-left corner to right-bottom corner.

- (4) For one element, the MQD in the element is encoded by higher-level corresponding MQD or Qmax first. If the element belongs to bands on the top level, the MQD is encoded by Qmax; otherwise the MQD (x, y) is encoded by its

corresponding higher level MQD  $\left(\left|\frac{x}{2}\right|, \left|\frac{y}{2}\right|\right)$ . The four coefficients in the element are encoded by the MQD in the element second. The encoding sequence is top-left, top-right, bottom-left and bottom-right.

Figure 3.12 The encoding sequence of element encoding

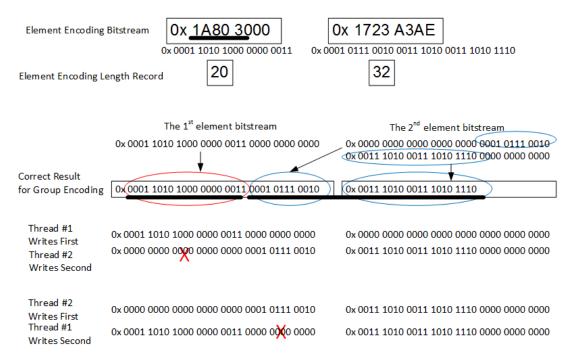

Different from sequential CPU encoding procedure, the result of parallel element encoding includes two arrays. One array, called element encoding bitstream, contains bitstreams of elements. Another array, called element encoding length record, records length of each element's bitstream, i.e. the number of bits used by each element bitstream.

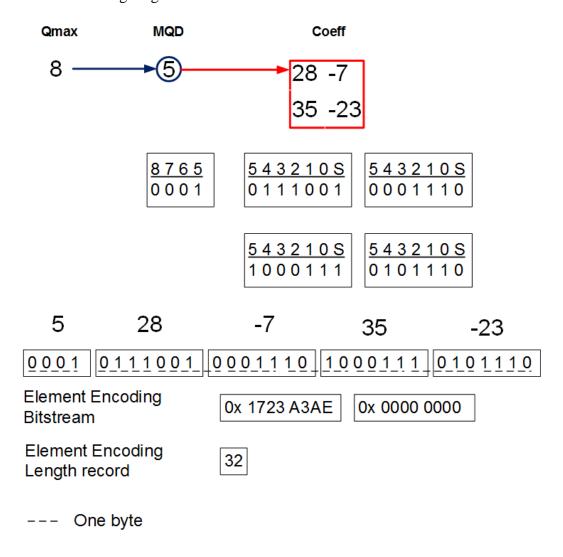

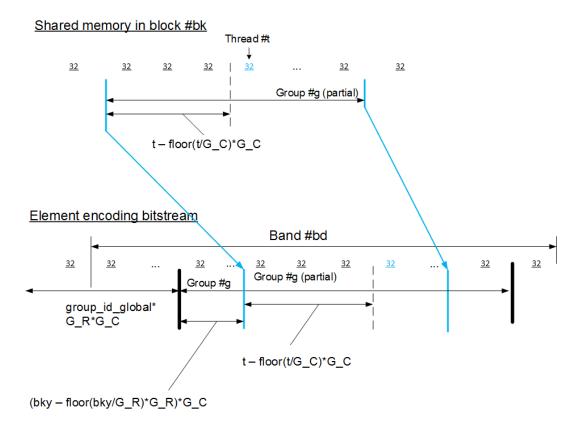

Figure 3.13 shows element encoding with Qmax. The "8 7 6 5" and "5 4 3 2 1 0" are bit index of coefficient's absolute value and "S" represents the bit index for coefficient's sign.

Element encoding with Qmax includes three steps:

- (1) The element's MQD ("5") is encoded by Qmax ("8")

- (2) Four coefficients corresponding to the MQD are encoded in the sequence of "top-left, top-right, bottom-left and bottom-right". i.e. "28, -7, 35, -23". The absolute value is encoded first, and the sign is encoded second.

- (3) The generated bitstream ("0x 1723 A3AF") is stored in element encoding bitstream and the number of bits used to encode this element, i.e. 32, is recorded in element encoding length record.

Figure 3.13 Example of element encoding with Qmax

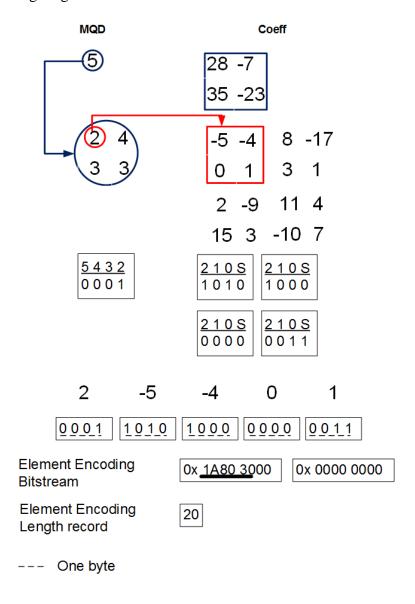

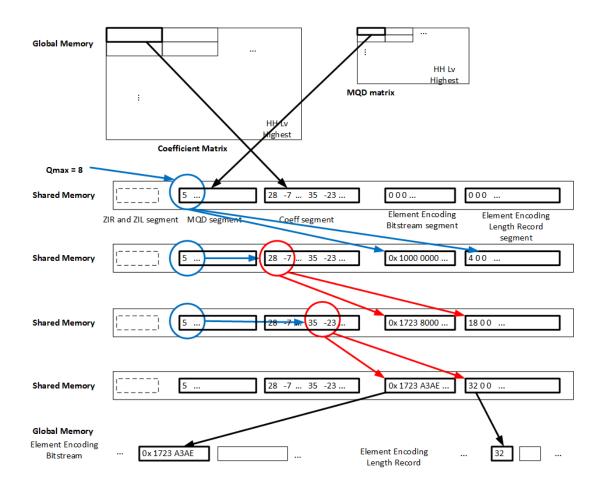

Figure 3.14 shows an example of element encoding with the higher-level MQD. Similarly, it contains three steps:

- (1) The element's MQD ("2") is encoded by higher-level MQD ("5")

- (2) Four coefficients corresponding to the MQD are encoded in the sequence of "top-left, top-right, bottom-left and bottom-right" ("-5, -4, 0, 1").

- (3) The generated bitstream ("0x 1A80 3") is stored in element encoding bitstream and the number of bits used to encode this element, i.e. 20, is recorded in element encoding length record.

## Figure 3.14 Example of element encoding with higher-level MQD